科技部工程司109年度產學計畫優良成果|民生化材領域

低應力無電鍍晶片堆疊之科技開發

計畫基本資料

編號:MOST 108-2622-E-002-001-CC2

執行單位:國立臺灣大學材料科學與工程學系暨研究所

主持人/共同主持人:高振宏/何政恩

參與人員:洪漢堂、楊竣翔、吳柏毅、翁億安、陳穎暄、楊清雲、高立宇、

馬振德、黃正豪、施柏紹

合作企業:欣興電子股份有限公司

文/圖:計畫團隊 編輯:張萬珍

計畫主持人高振宏教授(前排中)與實驗室團隊聚餐合影

近年來,藉由水平方向縮小線寬以提升電晶體密度日益困難,半導體業界轉而利用晶片堆疊(chip stacking)的方式在垂直方向尋求突破。此技術在堆疊的晶片之間會利用比覆晶接點(flip-chip joints)更小的微接點(micro joints)來連接上下的晶片,然而微接點的接合需要高溫,有些接法也需高壓,高溫與高壓帶來許多嚴峻的挑戰,如主流的接合製程迴銲及熱壓接合製程,迴銲製程中常會因為晶片受熱後翹曲導致外側接點虛銲,內側接點互連導致短路;熱壓接合製程係對晶片上下兩端外施加均勻的壓力,藉以抵抗晶片因不同材料熱脹冷縮程度不同而產生變形或是翹曲,但外加壓力的製程也同時帶來新的挑戰。

面對這棘手的難題,欣興電子公司結合國立臺灣大學高振宏教授與元智大學何政恩教授的團隊,採取廣泛用於生醫科技與微機電系統(micro-electro-mechanical systems, MEMS)製造微流道的polydimethylsiloxane (PDMS)科技與無電鍍製程,開發出一項能在低溫(< 100 °C)且完全不需要外加壓力的新型接合技術,能夠滿足目前封測技術往多功能異質整合、微型化、高集成密度及高效能的發展趨勢。由於這項技術還有無電鍍製程低溫及不加壓的優勢,將能應用至高階晶片端,提升產品良率及接合可靠度。高振宏教授指出,無電鍍技術在半導體製程中已是成熟的技術,常用於基板的表面處理,以達到抗腐蝕及阻礙擴散的目的,未來如果能將此低成本的技術應用於高階晶片端,可增加產品價值,提升臺灣電子產業界的競爭力道。

高教授指出,計畫最大的挑戰在於接合技術的均勻性是否能廣為業界所接受。他說:「當中任何一個接點失效,就等於技術無法應用於需要量產的業界。」同時,研究團隊還需探討不同無電鍍藥水上鍍的特性,排除反應的副產物氫氣,才可能達成高均勻性的接點。

這項計畫的研發成果部分在欣興電子公司的協助下開發了船槳式攪拌槽,並利用JCU Taiwan的電鍍藥水完成鍍製高均勻性圓弧(Dome-shaped)銅柱接點及平頭(Flat-topped)銅柱接點。為了能直接觀察無電鍍製程時氣泡的生成與優化鍍製參數,高教授的實驗室也開發glass wafer的整套試片製程。

在試片通道部分,圓弧銅柱接點利用金屬線定義液體流通試片的路徑,且在無電鍍反應後成功達成無孔洞生成之金屬鍍層;而平頭銅柱接點則是直接碰觸後進行無電鍍接合,可以有效縮短後續無電鍍接合時間近50 %。

在不同無電鍍鍍液系統部分,計畫團隊利用自行開發的無電鍍Ni藥水,在反應溫度80 ℃,反應時間30分鐘的條件下,成功達成高均勻性無電鍍Ni-P金屬化銜接,再藉由定量幫浦調整週期性間歇性流場(Periodic Intermittent Flow)有效排出副產物氫氣,解決無電鍍反應不均勻性沉積的問題。分析結果顯示,接點具有良好導電性,機械性質大於黏著層強度,且無電鍍Ni-P反應可以修飾表面不平整之銅柱,並在50 %接點錯位下仍能完整接合銅柱接點。

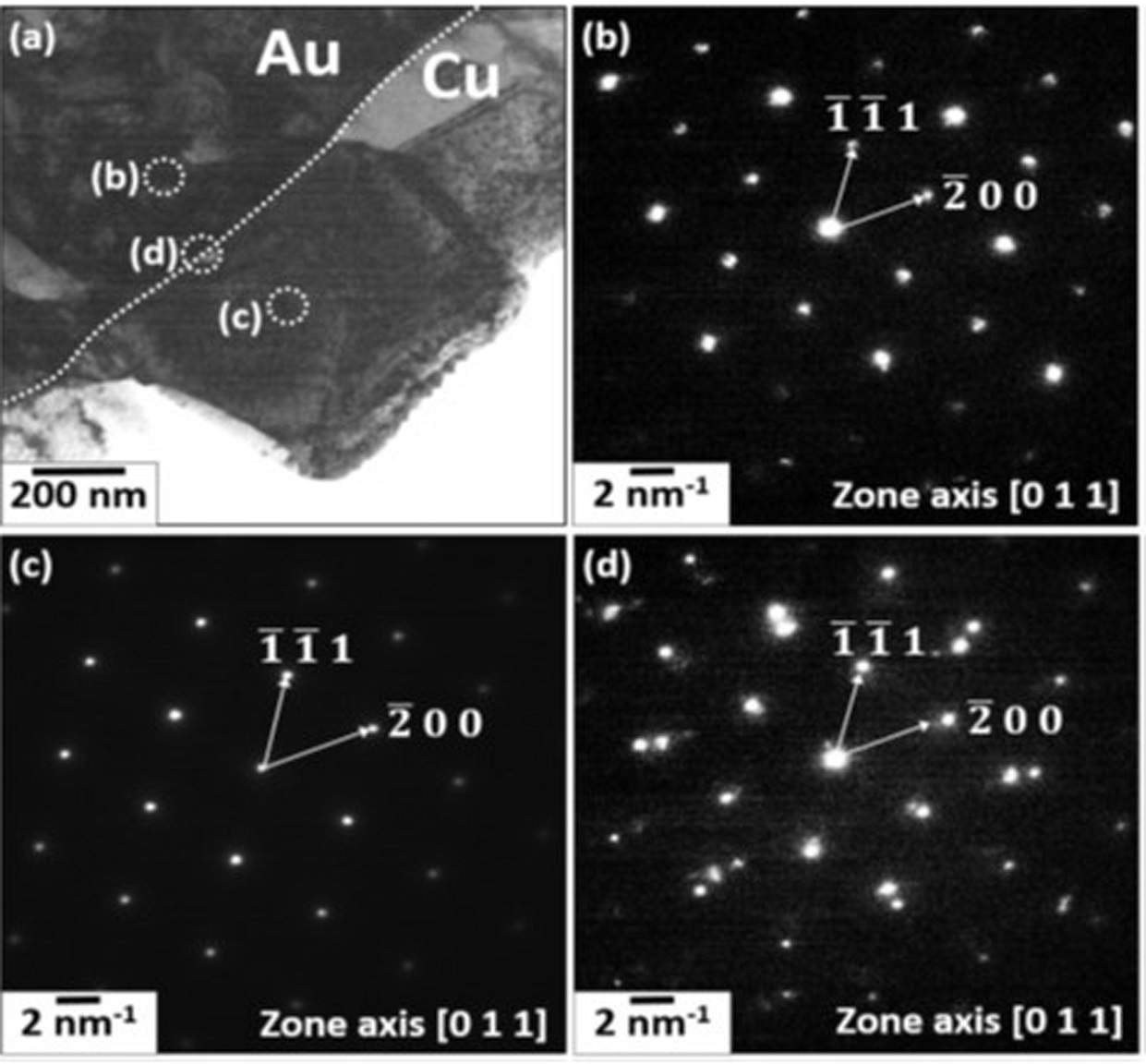

計畫團隊也成功利用臺灣上村提供的無電鍍Au藥水,在反應溫度50 ℃,反應時間4小時下完成高均勻性無電鍍Au金屬化銜接,在無電鍍Au直接置換金(DIG)表面處理的銅柱接合中,由TEM結果更發現銅柱上鍍的Au原子具有沿著銅柱表面晶體結構生長的特性,這項發現將可協助業界未來應用於更小接點尺寸下避免過度上鍍造成銅柱接點互連短路的問題。同時,高均勻性無電鍍Cu金屬化銜接也在使用臺灣上村提供的無電鍍Cu藥水,反應溫度50 ℃,反應時間30分鐘下成功接合。計畫團隊以實驗驗證結果顯示這兩種金屬化銜接接點皆具有良好導電性、機械強度和接點錯位容忍度。

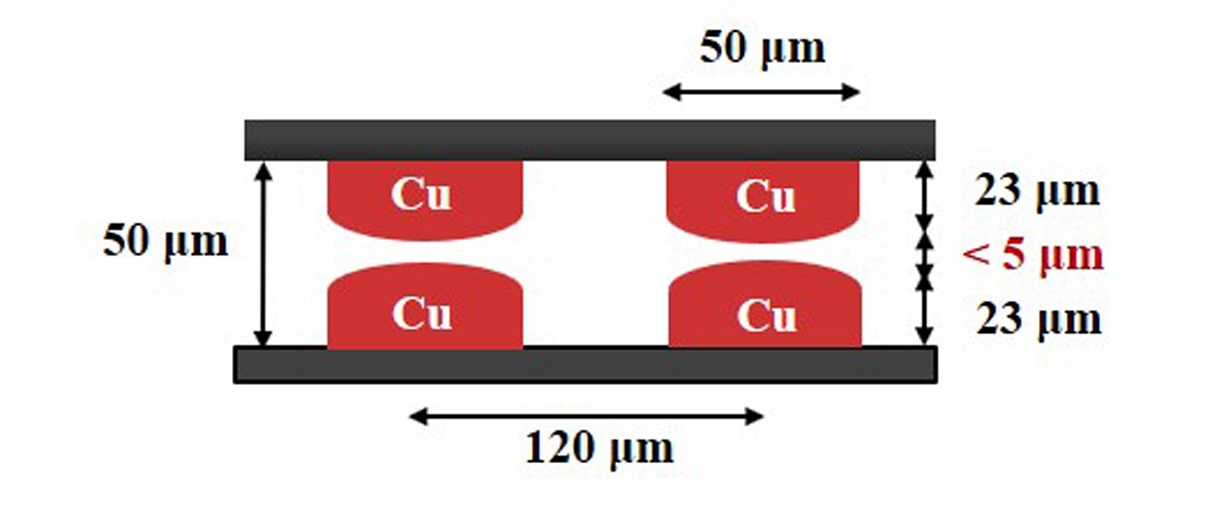

無電鍍微流道系統圖(國立臺灣大學材料系高振宏老師實驗室提供)

目前最小尺度無電鍍銅柱接點規格

(國立臺灣大學材料系高振宏老師實驗室提供)

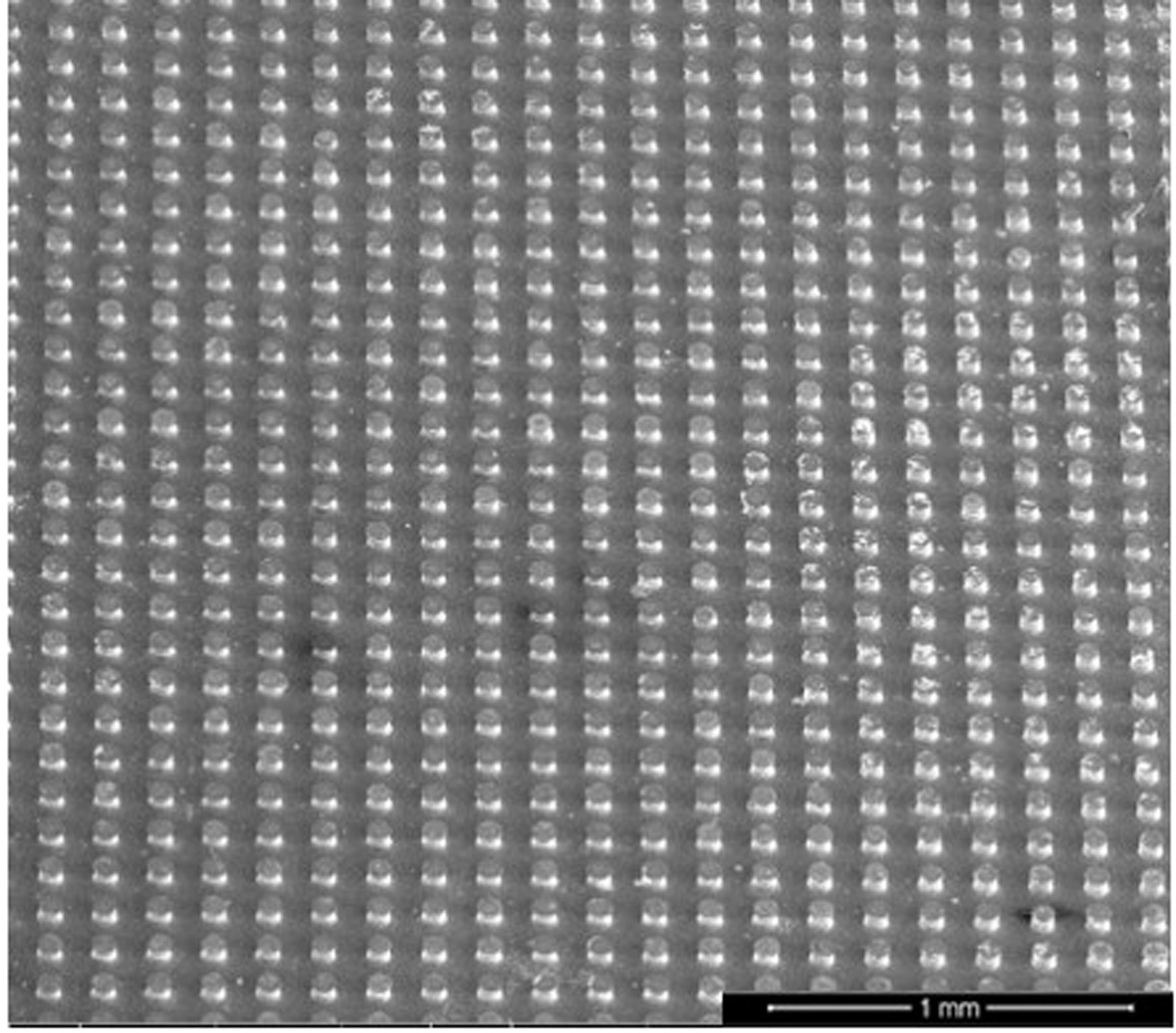

高均勻性無電鍍Ni-P金屬化銜接接點SEM圖

(國立臺灣大學材料系高振宏老師實驗室提供)

無電鍍Au金屬化銜接接點(DIG)之TEM分析圖

(國立臺灣大學材料系高振宏老師實驗室提供)

(a) TEM 明場下之Cu, Au界面image;(b) 座標(b)之選區繞射圖;(c) 座標(c)之選區繞射圖;(d) 座標(d)之選區繞射圖

高振宏教授團隊與欣興電子公司研發團隊首發互連結構及其製造方法,並積極開發至業界尺寸需求,此技術獲得:中華民國I 608771、I 643533、美國US 9786634 B2、US 10332861 B2等兩國發明專利(Interconnection Structures and Methods for Making the Same)及發表12篇SCI期刊論文,計畫的其他亮眼成果還包括:海報發表3次,其中2次分別獲得69屆ECTC最佳互動簡報獎及學生海報獎;會議期刊4篇,其中1篇獲得69屆ECTC最佳互動論文獎。

在人才培育的部分,本項計畫培育了7位碩士生及3位博士生,1位學生在執行計畫的過程中,激發其繼續攻讀博士班的意願,高教授相信,這些學生未來皆是相關領域的重要人才。同時,計畫的部分成果分別為1位博士生畢業論文及5位碩士生畢業論文。參與研究計畫開發的2位博士生楊竣翔與洪漢堂畢業後即進入台積電公司擔任研發要職,而參與研究的碩士生翁億安與陳穎暄,也分別至康寧玻璃及聯發科擔任要職。

高教授分享,本計畫還完成3項技術授權,他看到自己所帶領的研究團隊在技轉過程中,透過與欣興電子工程師交流的過程,迅速學習到業界目前無電鍍技術發展的近況,更能了解業界工程師做研究的態度,甚感欣慰。高教授也帶領研究團隊參與國內外學術會議,由於這套技術所包含的專業包羅萬象,透過交流,往往有意想不到的收穫。

經過計畫的淬煉,高振宏教授的實驗室與欣興電子公司的研發能量均向上提升,公司增進關鍵技術與自主研發的功力,強化高教授實驗室與業界的聯結,使實驗室的研究跨出純學術研究的範疇。

高教授結論,這項計畫結合學界的基礎知識及業界的技術方法,解決了合作企業在工業界遇到的各項挑戰,為無電鍍製程低溫及不加壓技術應用至高階晶片端奠定一定的基礎,更為目前封測技術朝向多功能異質整合、微型化、高集成密度及高效能需求增加一項解決方法,為臺灣電子產業界發展做出突破,他有信心,此技術的持續發展將讓電子產業的封裝技術邁向下一個里程碑。